# ALL INDIA 1<sup>st</sup> RANK 19 TIMES IN GATE &

## ALL INDIA 2<sup>nd</sup> RANK 10 TIMES IN GATE

## ACE EDUCTIONAL ACADEMY

H.O: 204, Rahman Plaza, Opp: Methodist School, Fernandez Hospital Lane, Abids, Hyderabad. Ph: 040 – 24752469 / 24750437

B.O: 201 A & B, Pancom Business Centre, Opp: J.C.Brothers, Ameerpet, Hyderbad. Ph: 040 - 65974465

website: www.aceenggacadmy.com email:ace.gateguru@gmail.com

## GATE - SYLLABUS

## **Digital Electronics & Mircroprocessors**

Transistor as a switching element; Boolean algebra, simplification of Boolean functions, Karnaugh Map and application; IC Logic gates and their characteristics; IC logic families: DTL,TTL, ECL, NMOS, PMOS and CMOS gates and their comparison; Combinational logic circuits; Half adder, full adder; Digital comparator; Multiplexer; ROM and their applications. Flip – flops, R – S, J – K, D and T flip – flops; Different types of counters and registers; waveform generators. A/D & D/A converters. Semiconductor memories. Microprocessor: Architecture, Programming, Memory and I/O Interfacing.

## **Digital Electronics & Microprocessors**

### **INDEX**

| Chapter No.                               | Contents                            | Page No.  |

|-------------------------------------------|-------------------------------------|-----------|

| 01                                        | Number Systems                      | 1 – 12    |

| 02                                        | Boolean Algebra & Karnaugh Maps     | 13 – 20   |

| 03                                        | Logic Gates                         | 21 – 27   |

| 04                                        | Logic Gate Families                 | 28 – 35   |

| 05                                        | Combinational Digital Circuits      | 36 – 41   |

| 06                                        | Sequential Digital Circuits         | 42 – 46   |

| 07                                        | Semiconductor Memories              | 47 – 50   |

| 08                                        | A/D & D/A Converters                | 51 – 53   |

|                                           | Previous GATE Questions (Digital)   | 54 – 85   |

| 09                                        | 09 Introduction to Microprocessors  |           |

| Previous GATE Questions (Microprocessors) |                                     | 113 – 133 |

| 10                                        | Public Sector Examination Questions | 134 – 144 |

Managing Director

Y.V. GOPALA KRISHNA MURTHY

#### **Profile**

S. V. Rao, B.Sc., B.Tech., M.E.(Digital Systems)., M.I.S.T.E., has been working for over 22 years, including the last 11 + years in the VLSI industry. Before joining the VLSI industry in 2000, he taught in the department of Electronics and Communication Engineering, MVSR Engineering College as an Associate Professor. He has also taught at the University College of Engineering, Osmania University and JNTU College of Engineering, Hyderabad and worked as a Lecturer at Deccan College of Engineering & Technology, Hyderabad.

Rao has authored a book called "Computer Fundamentals and Applications" (RPH-1994) for Diploma Course in Polytechnics in Andhra Pradesh. He has also written a paper titled "Performance Evaluation of Non-Linear Edge Detectors in Digital Image Processing" which was presented at the "International Conference on Remote Sensing" organized by JNTU, Hyderabad in December 1994. The paper was subsequently published in the International Journal for Remote Sensing in 1995.

Sri S.V. Rao's contribution in the preparation of the booklet "Digital Electronics & Microprocessor" useful for all the competitive exams in Engineering is highly appreciated, as a social responsibility towards helping the Engineering students to achieve their goals.

#### Acknowledgements

I am grateful to Mrs. S.A. Lakshmi, who read the entire manuscript, prepared the softcopy and edited the material. I am pleased to acknowledge my indebtedness to Mr. Brahmaiah, who prepared diagrams and alignment of the data. Though no stone is left unturned in an attempt to eliminate the printing mistakes, yet some mistakes may crop up. Any suggestions indicating such mistakes are most welcome. Any constructive comments, suggestions, criticism from students and readers will be highly appreciated and can be mailed to somarouthu9@yahoo.co.in

#### **CIVIL ENGINEERING TOPPERS**

| S.NO | STUDENT NAME      | GATE H.T NO | RANK |

|------|-------------------|-------------|------|

| 01   | SATHISH.T         | CE 1620834  | 1    |

| 02   | NETAJI PRASAD.В   | CE6920096   | 2    |

| 03   | A.BHASKER         | CE1430312   | 3    |

| 04   | MOHD.ATAULAH KHAN | CE1430072   | 5    |

| 05   | CH.J.P.SREE RAM   | CE6690202   | 10   |

### MECHANICAL ENGINEERING TOPPERS

| S.NO | STUDENT NAME          | GATE H.T NO | RANK |

|------|-----------------------|-------------|------|

| 01   | DESAI HARDIKKUMAR .G. | ME1500007   | 7    |

| 02   | K.VENKATACHALAPATHI   | ME1500093   | 9    |

### COMPUTER SCIENCE & ENGINEERING TOPPERS

| S.NO | STUDENT NAME        | GATE H.T NO | RANK |

|------|---------------------|-------------|------|

| 01   | JITHIN VACHARY      | CS7580245   | 2    |

| 02   | VENKATASATYAKIRAN.D | CS1540009   | 10   |

#### **ELECTRICAL ENGINEERING TOPPERS**

| S.NO | STUDENT NAME        | GATE H.T NO | RANK            |

|------|---------------------|-------------|-----------------|

| 01   | ANIL KUMAR A.       | EE6240284   | 2 (Test series) |

| 02   | GIRISH KUMAR DASARI | EE6760582   | 7 (Test series) |

| 01   | V. NARASIMHAMURTHY  | EE7640633   | 13              |

| 02   | M. NAGARAJU REDDY   | EE7630195   | 14              |

| 03   | THOKARE NITHIN.D    | EE1600530   | 18              |

#### **ELECTRONICS & COMMUNICATION ENGINEERING TOPPERS**

| S.NO | STUDENT NAME           | GATE H.T NO | RANK |

|------|------------------------|-------------|------|

| 01   | M.YESHWANTH            | EC1440615   | 9    |

| 02   | SANDEEP SHARATH WAIKER | EC1460408   | 11   |

| 03   | VENKATESH SASANAPURI   | EC1490210   | 16   |

#### INSTRUMENTATION ENGINEERING TOPPERS

| S.NO | STUDENT NAME       | GATE H.T NO | RANK |

|------|--------------------|-------------|------|

| 01   | MAHESH RAVI VARMA  | IN1570571   | 2    |

| 02   | MD ABDUL RAZAK     | IN1570385   | 3    |

| 03   | MAHESHWARI RUTHIKA | IN2300299   | 6    |

#### Chapter 1

#### **Number Systems**

The concept of counting is as old as the evolution of man on this earth. The number systems are used to quantify the magnitude of something. One way of quantifying the magnitude of something is by proportional values. This is called analog representation. The other way of representation of any quantity is numerical (Digital). There are many number systems are present. The most frequently used number systems in the applications of Digital Computers are Binary Number System, Octal Number System, Decimal Number System and Hexadecimal Number System.

Base or Radix (r) of a Number System: The Base or Radix of a number system is defined as the number of different symbols (Digits or Characters) used in that number system.

The radix of Binary number system = 2 i.e. it uses two different symbols 0 and 1 to write the number sequence.

The radix of Octal number system = 8 i.e. it uses eight different symbols 0,1,2,3,4,5,6 and 7 to write number sequence.

The radix of Decimal number system = 10 i.e. it uses ten different symbols 0,1,2,3,4,5,6,7,8 and 9 to write number sequence.

The radix of Hexadecimal number system = 16 i.e. it uses sixteen different symbols 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E and F to write the number sequence.

The radix of Ternary number system = 3 i.e. it uses three different symbols 0,1 and 2 to write the number sequence.

To distinguish one number system from the other, the radix of the number system is used as suffix to that number.

Eg: 10<sub>2</sub> Binary Number.; 10<sub>8</sub> Octal Number;

10<sub>10</sub> Decimal Number; 10<sub>16</sub> Hexadecimal Number

Characteristics of any number system are:

- 1. Base or radix is equal to the number of digits in the system,

- 2. The largest value of digit is one (1) less than the radix, and

- 3. Each digit is multiplied by the base raised to the appropriate power depending upon the digit position.

The maximum value of digit in any number system is given by (r-1). Example: maximum value of digit in decimal number system = (10-1) = 9.

Binary, Octal, Decimal and Hexadecimal number systems are called positional number systems.

The number system in which the weight of each digit depends on its relative position within the number, is called positional number system.

Any positional number system can be expressed as sum of products of place value and the digit value.

Eg:

$$756_{10} = 7 \times 10^2 + 5 \times 10^1 + 6 \times 10^0$$

$$156.24_8 = 1 \times 8^2 + 5 \times 8^1 + 6 \times 8^0 + 2 \times 8^{-1} + 4 \times 8^{-2}$$

The place values or weights of different digits in a mixed decimal number are as follows:

The place values or weights of different digits in a mixed binary number are as follows:

The place values or weights of different digits in a mixed octal number are as follows:

The place values or weights of different digits in a mixed octal number are as follows:

Hexadecimal point

#### Decimal to binary conversion:

(a) Integer number: Divide the given decimal number repeatedly by 2 and collect the remainders. This must continue until the integer quotient becomes zero.

| T    |  |

|------|--|

| 1.2: |  |

.3710

| Quotient<br>37/2<br>18/2<br>9/2<br>4/2<br>2/2<br>1/2 | Remainder<br>18 + 1<br>9 + 0<br>4 + 1<br>2 + 0<br>1 + 0<br>0 + 1 |         |

|------------------------------------------------------|------------------------------------------------------------------|---------|

| 1/2                                                  | 0 + 1<br>∴ 37 <sub>10</sub> =                                    | 1001012 |

Note: The conversion from decimal integer to any base-r system is similar to the above example except that division is done by r instead of 2.

S V Rao

© Wiki Engineering

(b) Fractional number: The conversion of a decimal fraction to a binary is as follows:

```

Eg: 0.68755_{10} = X_2

```

First, 0.6875 is multiplied by 2 to give an integer and a fraction. The new fraction is multiplied by 2 to give a new integer and a new fraction. This process is continued until the fraction becomes 0 or until the number of digits has sufficient accuracy.

Integer value

ACE Academy

Eg:

$$0.6875 \times 2 = 1.3750 \times 1$$

$0.3750 \times 2 = 0.7500 \times 0$

$0.7500 \times 2 = 1.5000 \times 1$

$0.5000 \times 2 = 1.0000 \times 1$

$0.6875)_{10} = 0.1011_2$

NOTE: To convert a decimal fraction to a number expressed in base r, a similar procedure is used. Multiplication is by r instead of 2, and the coefficients found from the integers may range in value from 0 to (r-1).

The conversion of decimal number with both integer and fraction parts separately and then combining the results together.

Eg:

$$(41.6875)_{10} = x_2$$

$41_{10} = 101001_2 \ 0.6875_{10} = 0.1011$

Since  $(41.6875)_{10} = 101001.1011_2$ .

Eg: Convert the Decimal number to its Octal equivalent:  $153_{10} = X_8$

```

Integer quotient 153/8 = 19 +1 19/8 = 2 +3 2/8 = 0 +2 \cdot 153<sub>10</sub> = 231<sub>8</sub>.

```

Eg: Convert

$$253_{10}$$

to hexadecimal  $253/16 = 15 + (13 = D)$   $15/16 = 0 + (15 = F)$   $\therefore 253_{10} = FD_{16}$ .

Eg: Convert the Binary number  $101101_2$  to decimal.  $101101 = 2^5 \times 1 + 1 \times 2^4 + 1 \times 2^3 + 0 \times 2^1 + 1 \times 2^0$

= 32 + 8 + 4 + 1 = 45 $(101101)_2 = 45_{10}$ .

Eg: Convert the Octal number 2578 to decimal.  $257_8 = 2 \times 8^2 + 5 \times 8^1 + 7 \times 8^0 = 128 + 40 + 7 = 175_{10}$ .

Eg: Convert the Hexadecimal number IAF.23 to Decimal. IAF.23<sub>16</sub> = 1 X  $16^2$  + 10 X  $16^1$  + 15 X  $16^0$  + 2 X  $16^{-1}$  + 3 X  $16^{-2}$  =

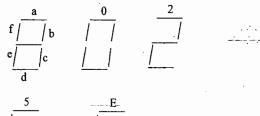

BCD (Binary Coded Decimal): In this each digit of the decimal number is represented by its four bit binary equivalent. It is also called natural BCD or 8421 code. It is a weighted code.

Excess-3 Code: This is an un weighted binary code used for decimal digits. Its code assignment is obtained from the corresponding value of BCD after the addition of 3.

BCO (Binary Coded Octal): In this each digit of the Octal number is represented by its three bit binary equivalent.

BCH (Binary Coded Hexadecimal): In this each digit of the hexadecimal number is represented by its four bit binary equivalent.

| Decimal<br>Digits                              | BCD<br>8421                                                                  | Excess-3                                                                     | Octal<br>digits                      | ВСО                                                  | Hexadecimal digits                                                      | ВСН                                                                                                                  |

|------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001 | 0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010<br>1011<br>1100 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>C<br>D<br>E | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1100<br>1010<br>1011<br>1100<br>1101<br>1111 |

Don't care values or unused states in BCD code are 1010, 1011, 1100, 1101, 1110, 1111.

Don't care values or unused states in excess-3 code are 0000, 0001, 0010, 1101,

The binary equivalent of a given decimal number is not equivalent to its BCD value. Eg:  $25_{10} = 11001_2$ .

The BCD equivalent of decimal number 25 = 00100101 from the above example the BCD value of a given decimal number is not equivalent to its straight binary value.

The BCO (Binary Coded Octal) value of a given Octal number is exactly equal to its straight binary value. Eg:  $25_8 = 21_{10} = 101101_2$

The BCO value of 25g is 010101.

-ACE Academy

From the above example, the BCO value of a given Octal number is same as binary equivalent of the same number.

The BCH (Binary Coded Hexadecimal) value of a given hexadecimal number is exactly equal to its straight binary.

Eg:

$$25_{16} = 37_{10} = 100101_2$$

The BCH value of hexadecimal number  $25_{16} = 00100101$ . From this example the above statement is true.

| (r-1)'s Complement r's Complement 2's 2's | Octal r = 8 r = 10 r = 10 9's 8 th's 10's | Hexadecimal<br>r = 16<br>15 <sup>th</sup> 's<br>16 <sup>th</sup> 's |

|-------------------------------------------|-------------------------------------------|---------------------------------------------------------------------|

|-------------------------------------------|-------------------------------------------|---------------------------------------------------------------------|

Rules of Binary addition: 0 + 0 = 0;

0+1=1:

1+0=1; 1+1=1 0

Rules of Binary subtraction: 0-0=0; 0-1=1 1; Borrow

Example: Add the two Binary numbers 101101<sub>2</sub>.

Augend 1 0 1 1 0 1

Addend 1 0 0 1 1 1

1-1-1-1 - ...

Sum 1010100

Example: Subtract the Binary number 1001112 from 1011012.

Minuend: 101101

Subtracted: -100111

Difference: 000110

www.raghul.org

Example: Multiply the Binary number 10112 with 1012.

Multiplicand: 1011 Multiplier: X 101

Example: 10011 ÷ 11

11) 10011 (110

Ouotient = 110Remainder = 1. **ACE Academy**

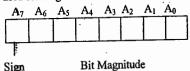

While storing the signed binary numbers in the internal registers of a digital computer, most significant bit position is always reserved for sign bit and the remaining bits are used for magnitude.

**Digital Electronics**

When the binary number is positive, the sign is represented by '0'. When the number is negative, the sign is represented by '1'.

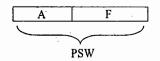

## Fixed-Point Representation and Floating Point Representation;

The representation of the decimal point (ordinary point) in a register is complicated by the fact that it is characterized by a position between two flip-flops in the register. There are two ways of specifying the position of the decimal point in a register.

(1) Fixed Point and (2) Floating Point.

The fixed point method assumes that the decimal point (or binary point) is always fixed in one position. The two positions most widely used are (1) a decimal point in the extreme left of the register to make the stored number a fraction, and (2) a decimal point in the extreme right of the register to make the stored number an integer.

| _ |                      |                     | • |

|---|----------------------|---------------------|---|

| • |                      | Fixed point integer | r |

|   | Fixed point fraction | Fixed point integer |   |

The floating-point representation uses a second register to store a number that designates the position of the decimal point in the first register.

Positive numbers are stored in the registers of digital computer in sign magnitude form only.

S V Rao

Negative numbers can be represented in one of three possible ways.

- 1. Signed-magnitude representation.

- 2. Signed-1's complement representation.

- 3. Signed-2's complement representation.

Example: +9

Signed -magnitude 0 0001001 (a) 1 000 1001 signed-magnitude

- (b) 1 111 0110 signed-1's complement , /

- (c) 1 111 0111 signed-2's complement

The 2's compliment of a given-binary number can be-formed by leaving all least significant zeros and the first non-zero digit unchanged, and then replacing 1's by 0's and 0's by 1's in all other higher significant digits.

Example: The 2's complement of 10011000<sub>2</sub> is 01101000.

Subtraction using 2's complement: Represent the negative numbers in signed 2's complement form, add the two numbers, including their sign bit, and discard any carry out of the most significant bit.

Since negative numbers are represented in 2's compliment form, negative results also obtained in signed 2's compliment form.

Example: 1's complement:

| +6 0000110  | -6 1111001                                      | +6 0000110 | - 6   | 1111001                           |

|-------------|-------------------------------------------------|------------|-------|-----------------------------------|

| +9 0001001  | +9 0001001                                      | -9 1110110 | - 9   | 1110110                           |

| +15 0001111 | +3 (1) 0000010<br><u>Carry +1</u><br>+3 0000011 | -3 1111100 | -15 ( | 1) 1101111<br>Carry +1<br>1110000 |

\* Example: 2's complement:

The advantage of signed 2's complement representation over the signed-1's compliment form (and the signed-magnitude form) is that it contains only one type of zero.

The range of binary integer numbers that can be accommodated in a register of length n-bits using signed-1's compliment form is given by  $+(2^{n+1}-1)$  to  $-(2^{n-1}-1)$  which includes both types of zero's i.e., +0 and -0. For example if n = 8, then range is +127to -127.

The range of integer binary numbers that can be accommodated in a register of n-bits length by using signed 2 s complement representation is given by  $+(2^{n-1}-1)$  to  $-2^{n-1}$  which includes only one type of zero i.e., +0. For example if n=8, then range is +127 to -128.

2's compliment form is usually chosen over 1's complement to avoid the occurrence of a negative zero. 2's compliment of zero is zero only.

The 1's complement of 1's compliment of a given number is the same number itself.

The general form of floating-point number is  $mr^e$ . Where M = Mantissa, r = base, e = exponent. Example:  $+0.3574 \times 10^5$ .

The Mantissa can be a fixed point fraction or fixed point integer.

Normalization: Getting non-zero digit in the most significant digit position of the mantissa is called Normalization.

If the floating point number is normalized, more number of significant digits can be stored, as a result accuracy can be improved.

A zero cannot be normalized because it does not contain a non-zero digit.

The hexadecimal code is widely used in digital systems because it is very convenient to enter binary data in a digital system using hexcode.

The parity of a digital word is used for detecting error in digital transmission.

Hollerith code is used for punched card data. -

In weighted codes, each position of the number has specific weight. The decimal value of a weighted code number is the algebraic sum of the weights of those positions in which 1's appears.

Most frequently used weighted codes are 8421, 2421 code, 5211 code and 84 2'1' code.

Example: The decimal number 493 is represented in different codes as

In 8421 code: 0010 1001 0011 In 2421 code: 0100 1111 0011 In 521'1' code: 0111 1111 0101 In 842'1' code: 0100 1111 0101

Reflective Code: A code is called reflective or self complimenting if the code for 9 is the compliment for the code for 0, code for 8 is the compliment from 1 and so on. 2421, 842'1', 5211 are examples for reflected codes.

Sequential Code: A code is called sequential if each successive code-is one binary number greater than its preceding code. Example: 8421

#### CHARACTERCODES:

ACE Academy

An alphanumeric code is a binary code of a group of elements consisting of the ten decimal digits, the 26 letters of the alphabet, and a certain number of special symbols such as .

The total number of elements in the alphanumeric group is greater than 36. Therefore it must be coded with a minimum of six bits  $(2^6 = 64)$ .

6-bit internal code is an alphanumeric code.

Most frequently used alphanumeric codes are

- (1) ASCII (American Standard Code for Information Interchange).

- (2) EBCDIC(Extended BCD Interchange Code).

ASCII is a 7-bit character code. For all practical purposes, an eight bit code is used because the eighth bit is invariably added for parity.

EBCDIC is an 8-bit character code. It uses ninth bit for parity.

When discrete information is transferred through punch cards, the alphanumeric characters use a 12-bit binary code.

Notes:

11

#### **EXERCISE**

| 1 | The number | system with rad | lix 2 is knowr | n as      |

|---|------------|-----------------|----------------|-----------|

|   | (a) Rinary | (b) Decimal     | (c) Octal      | (d) Hevad |

2 A group of four bits is known as (a) bit (b) byte (c) nibble (d) word

3 The knowledge of binary number system is required for the designers of computer and other digital systems because

(a) It is easy to learn binary number system

(b) It is easy to learn Boolean algebra

(c) It is easy to use binary codes

(d) The devices used in these systems operates in binary

4 The ones complement of the binary number 10001011 is (a) 01110100 (b) 11111111 (c) 01110101 (d) 11111110

5 The two complement of the number 100101000 is (a) 011010110 (b) 111111111 (c) 011010111

(d) None

6 The ones complement of ones complement of the given binary number is

(a) same binary number

(b) zero

(c) non-zero (d) none

7 The twos complement of the twos complement of the given binary number 1011001 is

(a) 1011000 (b) 1010110 (c) 1011001 (d) 0100111

8 The base or radix a Hexadecimal number system is

(a) 2

(b) 8

(c) 16

9 The number system with base or radix 8 is known as

(a) binary

(b) decimal

(c) octal

(d) hexadecimal

10 The decimal equivalent of the binary number 101101 is

(a) 48

(b) 45

(c) 57

(d) 75

11 The decimal equivalent of the binary number 1001.0101 is

(a) 9.125

(b) 9.6125

(c) 9.3125

(d) 9.6215

12 The binary equivalent of decimal number 255 is

(a) 11111110

(b) 11111101

(c) 11111111

(d) none

13 Identify the binary number represented by the decimal number 10.625

(a) 1010.011

(b) 1010.101

(c) 1010.110

(d) none

14 The binary equivalent of the decimal number 0.6875 is

(a) 0.1010

(b) 0.1011

(c) 0.1101

(d) 0.011<del>0</del>

S V Rao

ACE Academy **Number Systems** 15 The octal equivalent of the decimal number 375 is (a) 560 (b) 567 (c) 565 (d) none 16 The octal equivalent of the decimal number 27.125 is (a) 33.23 (b) 33.28 (c) 33.1 (d) 33.01 17 The decimal equivalent of the octal number 237 is (a) 159 (b) 165 (c) 162 (d) 160 18 The hexadecimal equivalent of the decimal number 375 is (a) 177 (b) 17A (c) 1A0 (d) none 19 The decimal equivalent of the hexadecimal number "BEED" is (a) 47877 (b) 48877 (c) 48777 (d) none 20 Encode the decimal number 327.87 in BCD code (a) 0011 0010 0111. 1000 1001 (b) 0011 0010 0110, 1001 1000 (c) 0011 0010 0111. 1100 1010 (d) none 21 The decimal equivalent of the hexadecimal number 3A.2F is (a) 58.1835 (b) 58.1385 (c) 58.23 (d) none 22 The decimal number 13 is represented in natural BCD as (a) 1101 (b) 0001 0011 (c) 0000 1101 (d) none 23 The binary equivalent of the hexadecimal number A0B5 is (a) 1010 0001 1011 0101 (b) 1010 0000 1010 0101 (c) 1010 0000 1011 0101 (d) none 24 The octal equivalent of the binary number 11010111 is (a) 656 (b) 327 (c) 653 (d) D7 25 The decimal equivalent of the binary number 110101111 is (b) 225 (c) 250(d) none

26 The octal equivalent of the decimal number 215 is (a) 327

(b) 372

(c) 237

27 The maximum positive and negative numbers which can be represented in twos complement form using n bits are respectively

(a)  $+(2^{n-1}-1), -(2^{n-1}-1)$ (c)  $+2^{n-1}$ ,  $-2^{n-1}$

(b)  $+(2^{n-1}-1)$ ,  $-2^{n-1}$  $(d) + 2^{n-1}, -(2^{n-1} + 1)$

28 When two n-bit binary numbers are added then the sum will contain at the most

(a) n-bit

(b) (n+1)-bits

(c) (n+2)-bits

(d) (n+n)-bits

29 The largest positive number that can be stored in a computer that has 16-bit word length and uses twos complement arithmetic is

(a) 32

(b) 32767

(c) 32768

(d) 65536

30 The maximum positive and negative numbers that can be represented in ones complement using n-bits are respectively

(a)

$$+(2^{n-1}-1)$$

and  $-(2^{n-1}-1)$

(c)  $+2^{n-1}$  and  $-(2^{n-1}-1)$

(b)

$$+(2^{n-1}-1)$$

and  $-2^{n-1}$

(c)

$$+2^{n-1}$$

and  $-(2^{n-1}-1)$

(d) None of these

#### **KEY**

#### POINTS TO REMEMBER

Chapter 2:

- → Boolean algebra works with binary variables.

- → A Boolean algebra is an algebraic system consisting of the set {0,1}, the binary operations called OR, AND, or NOT denoted by the symbols "+", ".", and "prime".

- → Boolean algebra enables the logic designer to simplify the circuit used, achieving economy of Construction and reliability of operation.

- → Boolean algebra suggests the economic and straightforward way of describing the circuitry used in any computer system.

- → Boolean algebra is unique in the way that; it takes only two different values either 0 or 1. It does not have negative number. It does not have fraction number.

- → The basic Boolean postulates:

Logical Multiplications based on AND function.

$$1.0.0 = 0$$

$$2.0.1 = 0$$

$$3.1.0 = 0$$

$$4.1.1 = 1$$

Logical Additions based on OR function

$$1.0+0=0$$

$$2.0 + 1 = 1$$

$$3.1+0=1$$

$$4.1 + 1 = 1$$

Complement based on NOT function.

9.

$$0' = 1$$

$$10.1' = 0$$

- → Boolean properties :

- a) Properties of AND function

$$1. X.0 = 0$$

$$2.0.X = 0$$

$$3. X.1 = X$$

$$4.1.X = X$$

b) Properties of OR function

$$5. X + 0 = X$$

$$6.0 + X = X$$

$$7. X + 1 = 1$$

$$8.1 + X = 1$$

c) Combining a variable with itself or its complement

**Digital Electronics**

9.

$$X.X' = 0$$

$$10. X.X = X$$

$$11. X + X = X$$

12.

$$X + X' = 1$$

$$13.(X')' = X$$

$$14. x.y = y.x$$

$$15. x + y = y + x$$

e) Distributive laws:

16.

$$x(y+z) = x.y + x.z$$

17.  $x+y.z = (x+y)(x+z)$

f) Associative laws:

18.

$$x(y.z) = (x.y)z$$

19.  $x+(y+z) = (x+y)+z$

g) Absorption laws:

$$20. x + xy = x$$

$$21. x(x + y) = x$$

$$22. x + x'y = x + y$$

23.

$$x(x' + y) = xy$$

h) Demorgan's laws.

24.

$$(x + y)' = x' \cdot y'$$

$$25. (x.y)' = x' + y'$$

S V Rao

© Wiki Engineering

→ In Boolean algebra '1' is called multiplicative identity and '0' is called additive identity.

Boolean Algebra & Karnaugh Maps

→ Literal: A primed or unprimed Boolean variable is called literal. Each variable can have maximum of two literals. Example: x is a variable which can have two literals x and x'.

Proof for some important properties:

**ACE Academy**

17.

$$x+yz = (x+y)(x+z)$$

$(x+y)(x+z) = x.x + x.z + x.y + y.z$

$= x + xz + xy + yz$

$= x(1+z)+xy+yz$

$= x+xy+yz$  since  $(1+z) = 1$

$= x(1+y) + yz = x + yz$  since  $(1+y) = 1$

22.

$$x + x'y = x+y$$

$x + x'y = (x+x')(x+y) = x+y$ .

23.

$$x(x'+y) = xy$$

$x(x+y) = xx' + xy = 0 + xy = xy$

- → Logic Circuits can be simplified by simplifying the Boolean equation using any one of the following methods:

- a) Applying Boolean properties

- b) Karnaugh-map method of simplification

- c) Tabulation method.

- → Boolean properties can be applied successively to minimize the given Boolean equations. But there is no guarantee that always we get minimal equation in this method.

- → 2,3 and 4 variable equations can be simplified to minimal value quickly using K-map method.

- → Tabulation method is used to minimize the equations with high order variables.

- → The properties of Boolean Algebra are useful for the simplification of Boolean equation leading to minimal gate structure.

- $\rightarrow$  Simplify the Boolean equation z = xy + x'(x + y).

$$xy + x'(x + y) = xy + x'.x + x'y = xy + x'y$$

=  $(x + x')y = y$ .

→ Duality Principle: The important property of Boolean algebra is the duality principle. "It states that every algebraic expression deducible from theorems of Boolean algebra remains valid if the operators and identify elements are interchanged. Examples:

**Digital Electronics**

**ACE Academy**

| X+X=X                 | x.x = x       | by duality |

|-----------------------|---------------|------------|

| x+1=1                 | x.0 = 0       | by duality |

| x+xy=x                | x(x+y) = x    | by duality |

| x+y=y+x               | xy = yx       | by duality |

| x + (y+z) = (x+y) + z | x(yz) = (xy)z | by duality |

- → The dual of the exclusive OR is equal to its complement.

- → A simple procedure to find the complement of a function is to take the dual of the function and complement each literal.

- → Standard product or a minterm (m): Consider two binary variables x and y combined with an AND operation. Since each variable appears in direct form or in its complement form there are four possible combinations. X' Y', X' Y, XY' and XY. Each of these four AND terms is called a minterm or a standard product term.

| Х | Υ | minter | n (m)          |

|---|---|--------|----------------|

| 0 | 0 | X'Y'   | m <sub>0</sub> |

| 0 | 1 | Χ'Y    | m <sub>1</sub> |

| 1 | 0 | XY'    | $m_2$          |

| 1 | 1 | XY     | m <sub>3</sub> |

→ Standard sum or Maxterm (M): Two binary variables x and y combined with an OR operation we will get four possible combinations X + Y, X + Y', X' + Y and X'+Y'. Each of these four OR terms is called a maxterm or a standard sum term.

| Y | Maxterm (M)            |

|---|------------------------|

| 0 | X + Y M <sub>0</sub>   |

| 1 | X + Y' M <sub>1</sub>  |

| 0 | X' + Y M <sub>2</sub>  |

| 1 | X' + Y' M <sub>3</sub> |

|   | Y 0 1 0 1              |

→ Maxterm is the compliment of its corresponding Minterm and vise versa.

Eg: XY = minterm.

The compliment of minterm = (XY)' = X' + Y' = maxterm

(SSOP) or Standard Product of Sums form(SPOS) is called Canonical form.

→ Canonical form: Expressing the Boolean function in Standard Sum of Product form

→ A Boolean function may be expressed algebraically from a given truth table by forming a minterm for each combination of the variables which produces a 1 in the function, and then taking the OR of all those terms.

| X   | Y | F |

|-----|---|---|

| 0   | 0 | 0 |

| 0 . | 1 | 1 |

| 1   | 0 | 1 |

| 1   | 1 | 0 |

$F(X,Y) = XY' + X'Y = \sum m(1,2)$ . This representation is called SSOP form.

→ A Boolean function may be expressed algebraically from a given truth table by forming the maxterms for each combination of the variables which produces zero '0' in the function, and then taking the AND of all those terms.

| İ | X | Y  | F |

|---|---|----|---|

|   | 0 | 0  | 0 |

|   | 0 | 1. | 1 |

| i | 1 | 0  | 1 |

|   | 1 | 1  | 0 |

$F = (X + Y)(X' + Y') = \prod M(0,3).$ This representation is called SPOS form.

→ If one canonical form is given it is possible to express other canonical form. Example: The other canonical form of the equation  $F(X,Y,Z) = \prod M(0,2,3,6)$  is

$$F(X,Y,Z) = \sum m(1,4,5,7).$$

→ Sum of all the minters of a given Boolean function is equal to 1.

Example:

$$(X,Y,Z) = \sum m(0,1,2,3,4,5,6,7) = 1$$

→ Product of all the maxterms of a given Boolean function is equal to 0.

Example:

$$F(X,Y,Z) = \Pi M(0,1,2,3,4,5,6,7) = 0.$$

- → Boolean functions expressed as a sum of minterms or product of maxterms are said to be in canonical form.

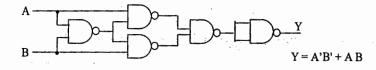

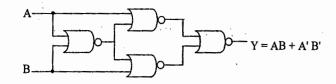

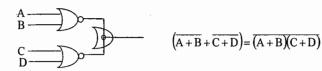

- → Sum of products form can be implemented by using two-level gate network NAND-NAND logic.

- → NAND-NAND realization is same as AND-OR.

- → Product of sums form can be implemented by using two-level gate network NOR-NOR logic.

- → NOR-NOR realization is same as OR-AND.

- → If the signals are propagating through two stages of gates, then it is called two level gate network.

- → Degenerative Form: A two level gate network is said to be degenerative if it degenerates to a single operation.

Example: AND - AND is equivalent to AND

→ The following two level gate networks are Degenerative forms:

| AND - AND  | AND  |

|------------|------|

| OR - OR    | OR   |

| OR - NOR   | NOR  |

| AND - NAND | NAND |

| NOR - NAND | OR   |

| NAND - NOR | AND  |

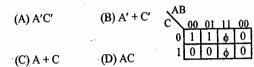

#### KARNAUGH MAPS (K-maps):

- → A map is a diagram made up of squares. Each square represents either a minterm or a maxterms.

- $\rightarrow$  The number of squares in the Karnaugh map is given by  $2^n$  where n = number of variable.

- → Two variable K-map consists of 4-cells or squares.

- → Three variable K-map consists of 8-squares or 8 cells.

- → Four variable K-map consists of 16-squares or 16 cells.

- → To maintain adjacency property Gray code sequence is used in K-maps. (Any two adjacent cells will differ by only one bit).

#### S V Rao

#### ~ . ..

→ Two variable K-map:

Each cell represents a term of two literals.

Grouping two adjacent (pair) squares containing I's represents a term of one literal.

Grouping four adjacent squares containing 1's represent the function = 1.

#### → Three variable K-map:

| YZ     | , 00     | 01 | 11 | 10 |

|--------|----------|----|----|----|

| $\chi$ |          |    |    |    |

|        | <u> </u> |    | ·  |    |

|        |          |    |    |    |

Each cell represents a term of three literals.

Grouping two adjacent cells containing 1's (Pair) represent a term of two literals.

Grouping four adjacent cells containing 1's (Quad) represent a term of one literal.

Grouping eight adjacent cells containing 1's represents the function =1.

#### → Four variable K-map:

| WX\YZ 00 01 11 10 |  |  |  |  |  |

|-------------------|--|--|--|--|--|

|                   |  |  |  |  |  |

|                   |  |  |  |  |  |

|                   |  |  |  |  |  |

|                   |  |  |  |  |  |

- → Each cell or square represents one minterm, giving a term of four literals.

- → Grouping two adjacent squares containing 1's represents a term of three literals.

- → Grouping four adjacent squares containing 1's represents a term of two literals.

- → Grouping eight adjacent squares containing 1's represents a term of one literal.

- → Grouping sixteen adjacent squares containing 1's represent the function = 1. (a term of zero literals).

- → Rules to simplify K-maps: 1.At the time of grouping the adjacent cells containing 1's always use maximum possible group. 2. All the cells containing 1's must be covered at least once in any group. 3. At the time of grouping don't care (X) values can be taken as 1's. 4. All don't care values need not be covered.

- → Tabulation method is used to simplify Boolean expressions when there are more than 5 variables.

- → In an n-variable K-map combining 8 adjacent cells containing 1's as a group will result a term of (n-3) literals.

- → In an n-variable K-map combining 8 adjacent cells containing 1's as a group will eliminate 3 variables.

| Number of variables | No. of cells<br>containing 1's<br>grouped | No. of variables eliminated | No. of literals present in the resulting term |

|---------------------|-------------------------------------------|-----------------------------|-----------------------------------------------|

| 2                   | 4                                         | 2                           | 0                                             |

|                     | 2                                         | 1                           | 1                                             |

| l · [               | 1                                         | 0                           | 2                                             |

| 3                   | 8                                         | 3                           | 0                                             |

| Γ                   | 4                                         | 2                           | 1                                             |

| ſ                   | 2                                         | 1                           | 2                                             |

|                     | 1                                         | 0                           | 3                                             |

| 4                   | 16                                        | 4                           | . 0                                           |

| . [                 | 8                                         | 3                           | 1                                             |

|                     | 4                                         | . 2                         | 2                                             |

|                     | 2                                         | 1                           | 3                                             |

|                     | 1                                         | Q                           | 4                                             |

→ Sum of Number of variables eliminated and number of literals present in the resulting term is always equal to the number of variables in the K-map.

#### POINTS TO REMEMBER

Chapter - 3

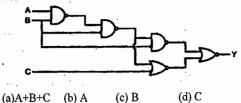

- → A gate is an electronic circuit with one output and one or more inputs. The output always depends on the input combinations.

- → AND, OR and NOT gates are called Basic gates.

- → NAND and NOR gates are called Universal gates, because, by using only NAND gates or by using only NOR gates we can realize any gate or any circuit.

- → Special gates are Exclusive-OR gate and Exclusive-NOR gate.

- → Exclusive-NOR (X-NOR) gate is also called inclusive-OR or gate of equivalence.

- → There are two types of logic systems:

- (a) Positive level logic system

- (b) Negative level logic system

- → Positive level logic system(PLLS): Out of the given two voltage levels, the more positive value is assumed as logic '1' and the other as logic '0'.

Example:

| Logic '0'               | Logic '1'                |

|-------------------------|--------------------------|

| 0V<br>-2V<br>-7V<br>+2V | 5V<br>+3V<br>- 2V<br>+7V |

→ Negative level logic system (NLLS): Out of the given two voltage levels, the more negative value is assumed as logic '1' and the other as logic '0'.

S V Rao

Example:

| Logic '1'                  | Logic '0                |

|----------------------------|-------------------------|

| 0V<br>- 2V<br>- 7V<br>+ 2V | 5V<br>+3V<br>-2V<br>+7V |

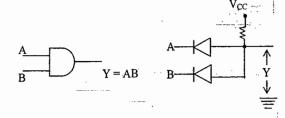

→ AND gate: "The output of AND gate is high if all the inputs are high." (or) "The output of AND gate is low if any one input is low or all the inputs are low."

| Truth Table |   |   |  |  |  |

|-------------|---|---|--|--|--|

| A           | В | Y |  |  |  |

| 0           | 0 | 0 |  |  |  |

| 0           | 1 | 0 |  |  |  |

| 1           | 0 | 0 |  |  |  |

| 1           | 1 | 1 |  |  |  |

Internal Circuit diagram of AND gate with positive level logic system.

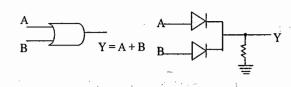

→ OR gate: "The output of an OR gate is high if any one input is high or all inputs are high." (or)

"The output of an OR gate is zero if all the inputs are zeros."

| Α  | В  | Y  |

|----|----|----|

| 0V | 0V | 0V |

| 0V | 5V | 0V |

| 5V | 0V | 0V |

| 5V | 5V | 5V |

Internal Circuit diagram of OR gate with positive level logic system

| Α | В | Y   |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | i | 1   |

| 1 | 0 | 1   |

| 1 | 1 | . 1 |

|   |   | 1   |

- → The circuit, which is working as AND gate with positive level logic system, will work as OR gate with negative level logic system.

- → The circuit, which is working as OR gate with positive level logic system, will work as AND/gate with negative level logic system.

- → Truth table is also called table of combinations.

- → The number of rows in the truth table is given by 2<sup>n</sup> where `n' is the number of inputs to the gate.

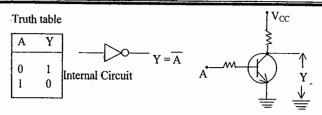

NOT gate: It is also called inverter. "The output of a NOT gate is always compliment of the input".

#### S V Rao

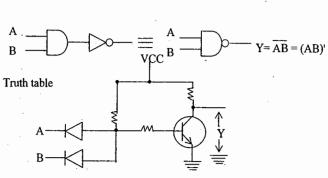

→ NAND gate: This is nothing but AND gate followed by NOT gate. "The output of NAND gate is high if any one input or all inputs are low."

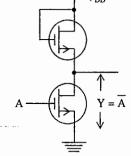

NAND with PLLS NOR with NLLS

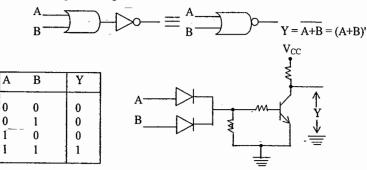

→ NOR gate: It is nothing but OR gate followed by NOT gate. "The output of NOR gate is high if all the inputs are low." (OR) "The output of NOR gate is low if any one input is high or all inputs are high."

NAND with PLLS NOR with NLLS

→ The circuit which is behaving as NAND gate with positive level logic system will behave as NOR gate with negative level logic system and vice – versa.

**ACE Academy**

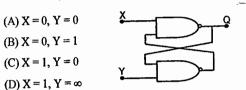

→ Exclusive-OR gate (X-OR): "The output of an X-OR gate is high for odd number of high inputs."

| <br>A<br>0<br>0 | B<br>0<br>1 | Y 0 | $A \xrightarrow{\qquad \qquad } Y = A \oplus B = AB' + A'B$ |

|-----------------|-------------|-----|-------------------------------------------------------------|

| 1               | 0<br>1      | 1 0 |                                                             |

→ Exclusive-NOR gate (X-NOR): It is X-OR followed by NOT. "The output is high for odd number of low inputs." (OR) "The output is high for even number of high inputs."

| A | ₿ | Y. | •••                    |   |                                |

|---|---|----|------------------------|---|--------------------------------|

| 0 | 0 | 1  | $(A \oplus B)' \equiv$ | B | $Y = A \odot B$ $= AB + A' B'$ |

| 1 | 0 | 1  | B 2                    |   |                                |

| 1 | 1 | 0  | ••                     |   |                                |

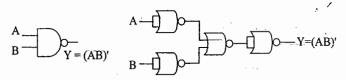

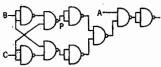

→ Realization of Basic gates using NAND and NOR gates:

1. NOR gate

NAND

NOR

$$A - \bigcirc O - Y = \overline{A}$$

$$A \xrightarrow{\qquad \qquad } Y = (A.A)' \qquad A \xrightarrow{\qquad \qquad } O \xrightarrow{\qquad } (A+A)' = A$$

$$A = A'$$

$Y = (A \cdot 1)'$

$A = A'$

$A = A'$

2. AND gate

© Wiki Engineering

3. OR Gate

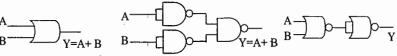

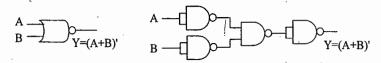

→ Realization of NAND gate using NOR gates:

→ Realization of NOR gate using NAND gates:

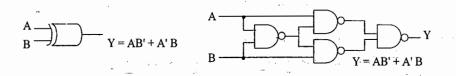

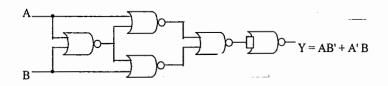

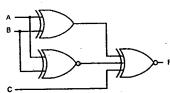

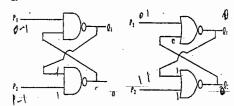

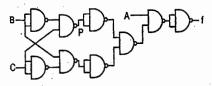

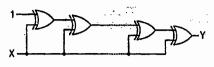

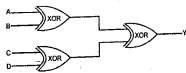

→ Realization of X-OR gate using NAND and NOR gates:

- → The minimum number of NAND gates required to realize X-OR gate is four.

- → The minimum number of NOR gates required to realize X-OR gate is five .

→ Realization of X-NOR gate using NAND and NOR gates:

$$\begin{array}{c} A \\ B \end{array} \longrightarrow \begin{array}{c} \\ \\ \end{array} \longrightarrow \begin{array}$$

- → The minimum number of NAND gates required to realize X-NOR gate is 5.

- → The minimum number of NOR gates required to realize X-NOR gate is 4.

- → Alternate logic gate symbols: The alternate logic gate symbols for the standard gate symbols are obtain by interchanging AND and OR symbols, and by inverting all inputs and outputs.

- → A bubbled NAND gate is equivalent to OR gate.

$$A \longrightarrow C$$

$B \longrightarrow C$

$Y = (A'B')' = A + B$

$A \longrightarrow C$

$Y = A + B$

→ A bubbled NOR gate is equivalent to AND gate

\* A bubbled AND gate is equivalent o NOR gate.

S V Rao

→ A bubbled OR gate is equivalent to NAND gate.

$$\begin{array}{ccc}

A & & & \\

B & & & \\

\end{array}$$

$$\begin{array}{ccc}

Y = (AB)' & = & A & \\

B & & & \\

\end{array}$$

$$\begin{array}{ccc}

Y = A' + B' = (AB)'$$

- → The alternate logic gate symbols for the standard gates are obtained based on Demorgan's laws only.

- → Equivalence Properties:

**ACE Academy**

$$1.(X \oplus Y)' = X'Y' + XY = X \odot Y$$

2.

$$X \odot 0 = X'$$

3.

$$X \odot 1 = X$$

4.

$$X \odot X = 1$$

5.

$$X' \odot X' = 0$$

6.

$$X \odot Y = X \odot Y$$

7.

$$(X \odot Y)' = X \oplus Y$$

Notes:

#### POINTS TO REMEMBER

- → Digital IC gates are classified not only by their logic operation, but also by the specific logic circuit family to which they belong. Each logic family has its own basic electronic circuit upon which more complex digital circuits and functions are developed.

- → Different types of logic gate families:

- RTL Resistor transistor logic gate family.

- DCTL Direct coupled Transistor Logic gate family.

- RCTL Resistor capacitor transistor logic.

- DTL Diode Transistor logic gate family.

- TTL Transistor Logic gate family.

- IIL Integrated injection Logic.

- HTL High Threshold Logic.

- ECL Emitter coupled logic.

- MOS Metal Oxide Semi-conductor.

- CMOS Complementary Metal Oxide Semi-conductor.

- → HTL is a modified form of DTL and IIL is a modified form of DCTL.

- → Because of high package density MOS and I<sup>2</sup>L logic gate families are used for Large Scale integration (LSI) functions.

- → TTL, ECL and CMOS are used for Medium Scale Integration (MSI) or Small Scale Integration (SSI).

- → Each logic gate family is identified with a series number. For example TTL family ICs are available in 74/54 series. CMOS IC's usually designated with 4000 series and ECL family with 10000 series.

- → RTL, DTL, ECL and 1<sup>2</sup>L Logic families uses bipolar transistors. Hence these families are called bipolar logic gate families.

- → MOS and CMOS families uses unipolar transistors called Metal-Oxide Semiconductor Field- effect Transistors (MOSFETs). Hence these families are called unipolar logic gate families.

- → Fan-out: "The number of standard loads that the output of the gate can drive without disturbing its normal operation".

- → Fan-in: "The maximum number of inputs that can be applied to the logic gate".

- -> Power dissipation: "The power consumed per gate".

ACE Academy

- → Propagation Delay: "The average transition delay time for the signal to propagate from input to output when the signals change in value".

- → Noise Margin: "It is the limit of a noise voltage which may be present without impairing the proper operation of the circuit"

- → Figure of Merit: The product of propagation delay time and power dissipation is known as figure of merit of performance of a gate. Normally minimum value is desired.

- → Logic Swing: The difference between the two output voltages (V <sub>OH</sub>-V<sub>OL</sub>) is known as the logic swing of the circuit.

- → Noise Immunity: "The ability to with stand variations in the input levels".

- → Saturation logic: A form of logic gates in which one output state is the saturation voltage level of the transistor. Example: RTL, DTL, TTL.

- → Unsaturated logic or Current Mode Logic: A form at logic with transistors operated outside the saturation region. Example: CML or ECL.

- → ECL has ultra-fast switching speed and low logic swing.

- → The temperature range of 74-series of TTL logic gate family is 0<sup>0</sup> C to 70<sup>0</sup> C. This series of IC's is used for commercial applications.

- → The temperature range of 54-series of TTL logic gate family is -55° C to 125° C. This series of IC's is used for Military applications.

- → Voltage parameters of the digital IC:

- High level input voltage,  $V_{IH}$ : This is the minimum input voltage which is recognized by the gate as logic 1.

- Low level input voltage,  $V_{IL}$ : This is the maximum input voltage which is recognized by the gate as logic 0.

- $\begin{array}{ll} \mbox{High-level output voltage, $V_{OH}$} & \mbox{This is the minimum voltage available at the output} \\ & \mbox{corresponding to logic 1.} \end{array}$

- Low-level output voltage, V<sub>OL</sub>. This is the maximum voltage available at the output corresponding to the logic 0.

- → The number of various functions available in a logic family is known as the breadth of the logic family.

- → When the outputs of logic gates are connected together additional logic functions are performed. This is known as wired logic.

- → When the outputs are available in complemented as well as uncomplemented form it is referred to as complementary outputs. This eliminates the need of using additional inverters.

- → Passive pull-up: In a bipolar logic circuit, a resistance R<sub>C</sub> used in the collector circuit of the output transistor is known as passive pull-up.

- → Active pull-up: In a bipolar logic circuit a BJT and diode circuit used in the collector circuit of the output transistor instead of R<sub>C</sub> is known as active pull-up. This facility is available is TTL family.

- → The advantages of active pull-up over passive-pull up are increased speed of operation and reduced power dissipation.

- → Open collector output: In a bipolar logic circuit if nothing is connected at the collector of the output transistor and this collector terminal is available as IC pin, it is known as open-collector output.

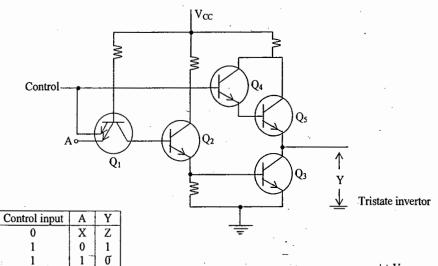

- → Tri-state logic: In the tri-state logic, in addition to low impedance 0 and 1 there is a third state known as the high-impedance state. When the gate is disabled it is in the third state.

- → In TTL logic gate family three different types of output configurations are available: they are Open collector output type. Totem-pole output type and tri-state output type.

- → The advantages of open-collector output type are wired-logic can be performed and loads other than the normal gates can be used.

- → The tri-state logic devices are used in bus oriented systems.

- → If any input of TTL circuit is left floating, it will function as if it is connected to logic 1 level.

- $\rightarrow$  The supply voltage range of 74-series is 5  $\pm$  0.25V and for 54-series is 5  $\pm$  0.5V.

- → Negative supply is preferred in ECL family because, the effect of noise present in the supply line is reduced considerably and any accidental short-circuiting of output to ground will not damage the gate.

- → MOS logic is mainly used for LSI and VLSI applications because the silicon chip area required for fabrication of a MOS device is very small.

- The fan-out of MOS logic gates is very high because of their high input impedance.

¥ V Rao

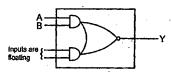

→ If any unused input terminal of a MOS gate is left unconnected, a large voltage may get induced at the unconnected input which may damage the gate.

**Logic Gates Families**

→ Different versions available in TTL logic gate family.

74/54 L : Low-power

74/54 H : High-power/ High-speed

74/54 LS: Low-power Schottky

74/54 S : Schottky

74/54 AS : Advanced Schottky

74/54 ALS: Advanced Low-power Schottky.

- → The supply voltage required for ECL logic family is -5.2V ± 10%.

- → Comparison of Different Logic Gate families:

| Fan-out            | DTL 7    | TTL<br>10 | ECL<br>25 | CMOS<br>50 | p-MOS<br>20  |

|--------------------|----------|-----------|-----------|------------|--------------|

| Propagation Delay  | 30n sec. | 10 nsec.  | 4 nsec.   | 70 nsec.   | 300 sec      |

| Power Dissipation  | 8mw      | 10mw      | 40mw      | 0.01mw.    | 0.2 - 10  mw |

| Noise Margin (min. | ) 700mV  | 400mV     | 200mV     | 300mV      | . 150mV      |

- → Fastest logic gate family is ECL. It is also called Current Mode Logic.

- → Slowest Logic gate family is CMOS.

- → The logic gate family, which consumes less power CMOS.

- → The logic gate family, which consumes more power ECL.

- → The logic gate family, which is having highest fan out CMOS.

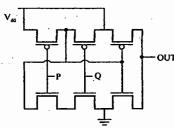

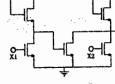

- → In CMOS circuits n-MOS transistor conducts if the gate to source voltage is more positive where as p-MOS conducts if gate to source voltage is more negative.

- → NMOS is faster than PMOS.

- → In tristate logic in addition to two low impedance outputs 0 and 1, there is third state known as high Impedance State.

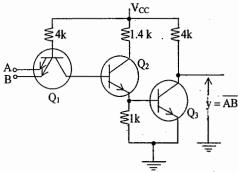

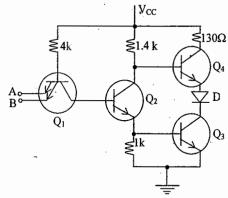

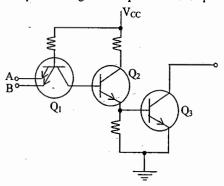

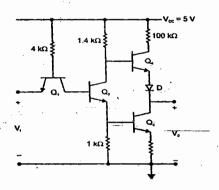

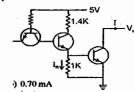

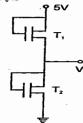

→ Standard 2 input TTL NAND gate

■ 2 – input NAND gate with Totem-pole output configuration

- The Dido de 'D' is used to keep the transistor Q4 in OFF stats when Q3 is in ON State.

- 2 input NAND gate with open collector output configuration.

• Gates with open collector output can be used for wired - AND operation.

**Logic Gates Families**

- Wired AND operation is equivalent to AND OR INVERT

- Tristate output configuration TTL circuit.

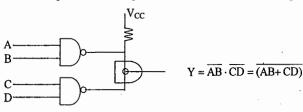

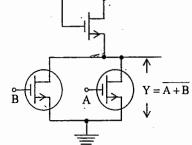

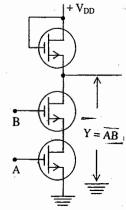

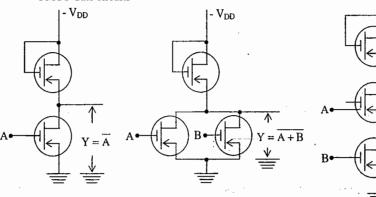

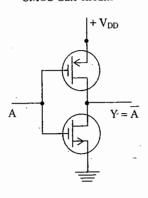

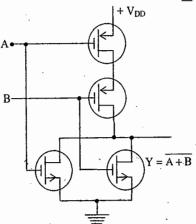

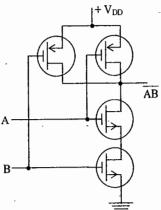

$+ V_{DD}$

$V_{DD}$

$Y = \overline{AB}$

PMOS Gate circuits

CMOS Gate circuits

S V Rao

Similar to open collector output in TTL, open emitter outputs are available in ECL.

The outputs of two or more ECL gates can be connected to get additional logic without using additional hardware. Wired – OR operation is possible with ECL ckts.

**Logic Gates Families**

- Wired OR operation is equivalent to OR AND INVERT

- If any input of an ECL gate is left unconnected, the corresponding E B junction will not be conducting. Hence it acts as if a logical 0 level voltage is applied to that input. i.e In ECL ICs, all unconnected/floating inputs are treated as logical OS.

Notes:

#### POINTS TO REMEMBER:

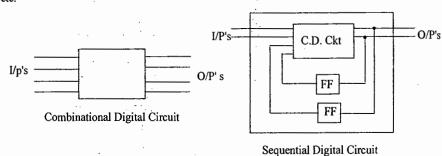

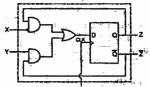

- → Digital circuits can be classified into two types :

- 1. Combinational digital circuits and

- 2. Sequential digital circuits.

- → Combinational Digital Circuits: In these circuits "the outputs at any instant of time depends on the inputs present at that instant only."

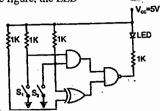

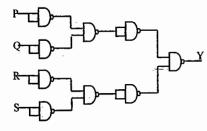

- → For the design of Combinational digital circuits Basic gates (AND, OR, NOT) or universal gates (NAND, NOR) are used.

Examples for combinational digital circuits are Half adder, Full adder, Half subtractor, Full subtractor, Code converter, Decoder, Multiplexer, Demultiplexer, Encoder, ROM, etc.

- → Sequential Digital Circuits: The outputs at any instant of time not only depends on the present inputs but also on the previous inputs or outputs.

For the design of these circuits in addition to gates we need one more element flip-flop.

- → Examples for sequential digital circuits are Registers, Shift register, Counters etc.

- → Half adder: A combinational circuit that performs the addition of two bits is called a half-adder. It consists of two inputs and two outputs.

| X | Y | Carry | Sum | $Sum = X \oplus Y = XY' + X'Y$ | XX                                   |

|---|---|-------|-----|--------------------------------|--------------------------------------|

| 0 | 0 | 0     | 0   | Carry = XY                     | $Y \longrightarrow Sum = X \oplus Y$ |

| 0 | 1 | 0     | 1   | X———Sum                        |                                      |

| 1 | 0 | 0     | 1   | Y H.A. Carry                   | , Carry = XY                         |

| I | 1 | 1     | 0   |                                |                                      |

|   |   |       |     |                                |                                      |

S V Rao

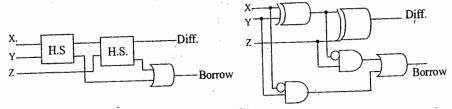

→ Half Subtractor: It is a Combinational circuit that subtracts two bits and produces their difference. It also has an output to specify if a 'l' has been borrowed.

| X                | Y                | Borrow      | Diff             | $Diff = X \oplus Y = XY' + X'Y$ | XX                           |

|------------------|------------------|-------------|------------------|---------------------------------|------------------------------|

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0<br>1<br>0 | 0<br>1<br>1<br>0 | Borrow = X'Y  X H.A.            | Y Diff. = X⊕Y  Borrow. = X'Y |

- → Half adder can be converted into half subtractor with an additional inverter.

- → Quarter Adder/Subtractor: The sum output of Half adder is called Quarter adder. The difference output of Half subtractor is called Quarter subtractor.

- → Quarter Adder/Subtractor is same as two input XOR gate.

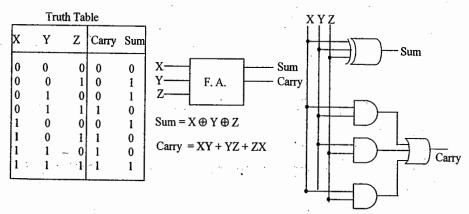

- → Full adder: It performs the addition of three bits (two significant bits and a previous carry) and generates sum and carry.

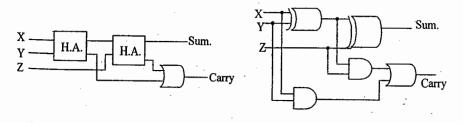

→ Full adder can be implemented by using two half adders and an OR gate.

**ACE Academy**

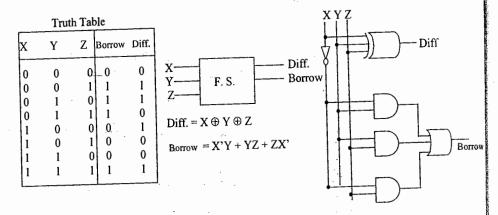

→ Full subtractor: It subtracts one bit from the other by taking previous borrow into account and generates difference and borrow.

Full subtractor can be implemented by using two half-subtractors and an OR gate.

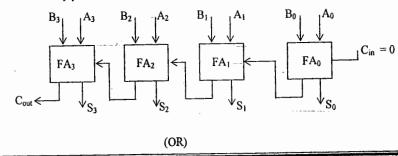

- → Four bit binary parallel adder can be constructed by using three full adders and one half adder or by using four full adders with input carry for least significant bit full adder is zero.

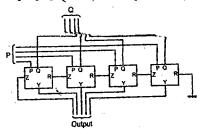

- → Four bit binary parallel adder shown in figure is also called as Ripple carry adder.

S V Rao

- → Carry Look-Ahead adder is faster than ripple carry adder.

- → Full adder is an example for 1-bit adder.

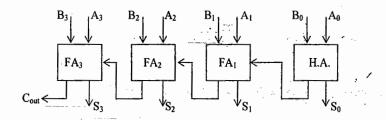

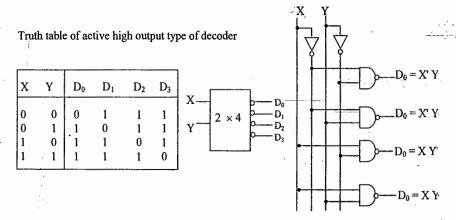

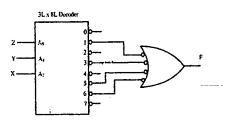

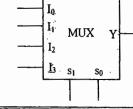

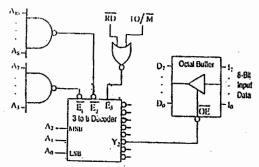

- → Decoder: A decoder is a logic circuit that converts an n-bit binary input code into M (2<sup>n</sup>) output lines such that each output line will be activated for only one of the possible combinations of inputs.

A decoder is a Combinational circuit that converts binary information from 'n' input lines to a maximum of  $2^n$  unique output lines.

Eg: 2 X 4 line Decoder (it is also called one of four line decoder).

- → Decoders are available in two different types of output forms: (1) Active high output type decoders and (2) active low output type of decoders.

- → Active high output type of decoders are constructed with AND gates and active low output type of decoders are constructed with NAND gates.

I = I

40

→ Activate low output type of decoders will give the output low for given input combination and all other outputs are high.

- → 3 to 8 line decoder is also called Binary-to-Octal decoder or converter. It is also called 1of-8 decoder, because only one of the 8 outputs is activated at a time.

- → Decoders are widely used in the memory system of a computer, where they respond to the address code input from the CPU to activate the memory storage location specified by the address code.

- → Decoders are also used to convert binary data to a form suitable for displaying on decimal read outs.

- → Decoders can be used to implement combinational circuits, Boolean functions etc.

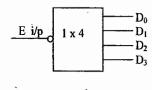

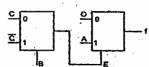

- → Demultiplexer: A decoder with enable input acts as a demultiplexer. "A demultiplexer is a circuit that receives information on a single line and transmits that information on one of 2<sup>n</sup> possible output lines. The selection of specific output line is controlled by the bit values of 'n' selection lines.

| E                     | Α                | В                     | D                | D                | D                | D                  |

|-----------------------|------------------|-----------------------|------------------|------------------|------------------|--------------------|

| 1<br>0<br>0<br>0<br>0 | X<br>0<br>0<br>1 | X<br>0<br>1<br>0<br>I | 0<br>1<br>0<br>0 | 0<br>0<br>1<br>0 | 0<br>0<br>0<br>1 | . 0<br>0<br>0<br>0 |

S V Rao

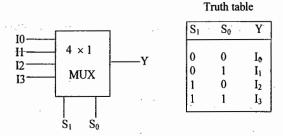

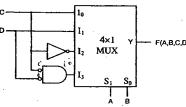

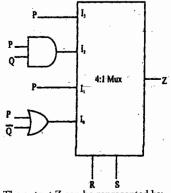

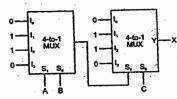

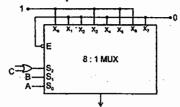

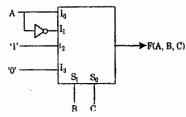

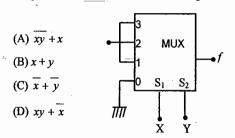

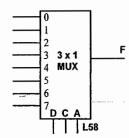

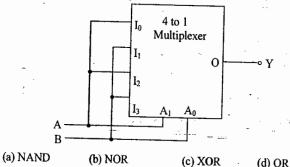

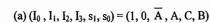

Multiplexer: Multiplexing means transmitting a large number of information units over a smaller number of channels or lines. "A digital multiplexer is a combinational circuit that selects binary information from one of many inputs lines and direct it a single output line. The selection of a particular line is controlled by a set of selection lines. Normally, there are 2<sup>n</sup> input lines and 'n' selection lines whose bit combinations determine which input is selected."

**Combinational Digital**

- → Multiplexers can be used for the implementation of Boolean functions, combinational circuits. They can also used for parallel to serial conversion.

- → Multiplexer is also called data selector or universal element.

- → All three variable Boolean equations can be implemented by using 8x1 multiplexer without using any additional gates. Some but not all three variable Boolean equations can also be implemented with 4x1 mux without using any additional gates.

- → Encoder: A decoder identifies a particular code present at the input terminals of the circuit. The inverse process is called Encoding. "An Encoder has number of inputs (2<sup>n</sup>) one and only one of which is in the high state or active, and an n-bit code is generated upon which of the inputs is excited.

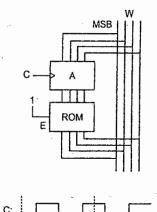

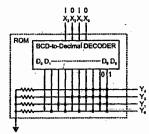

- → ROM (Read Only Memory): ROM is nothing but the combination of decoder and Encoder. It is a semi-conductor memory and which is a permanent memory. ROM can also be defined as a Simple Code conversion unit.

→ The memory which is constructed by using only gates is ROM.

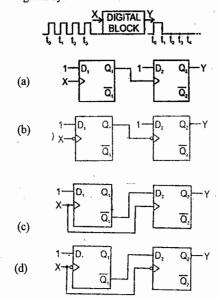

#### POINTS TO REMEMBER:

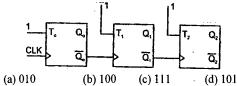

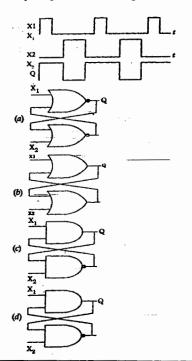

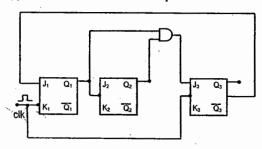

- → Two cross coupled inverters will form a basic latch which can store one bit of information.

- → Flip-Flops: Flip-Flop is also called Bistable multivibrator or binary. It can store one bit of information.

- → In a flip-flop one output is always complement of the other output.

- → Flip-Flop has two stable states.

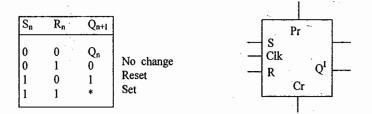

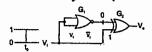

- → Clocked S-R Flip-flop: It is called Set-Reset Flip-Flop.

- → N<sub>1</sub> and N<sub>2</sub> from a basic latch. N<sub>3</sub> and N<sub>4</sub> are called Steering gates or Control gates, because they are used to control the outputs.

- → S-and R inputs are called synchronous inputs. Preset (Pr) and Clear (Cr) inputs are called direct inputs or asynchronous inputs.

- → The output of the flip-flop changes only during the clock pulse. In between clock pulses the output of the flip-flop does not change.

#### S V Rao

→ During normal operation of the flip-flop, preset and clear inputs must be always high.

ACE Academy

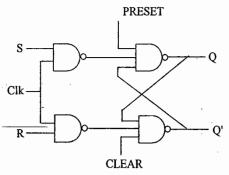

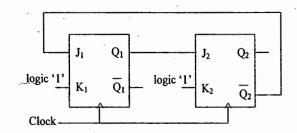

- → The disadvantage of S-R flip-flop is S = 1, R = 1 output can not be determined. This can be eliminated in j-k flip-flop.

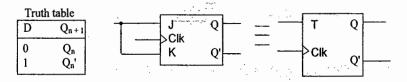

- → S R flip-flop can be converted to j k flip-flop by using the two equation S = JQ' and R = KO.

- $\rightarrow$  Race around problem is present in the j-k flip-flop, when both J = K = 1.

- → Toggling the output more than once during the clock pulse is called Race around Problem

- → The Race around problem in J-K flip-flop can be eliminated by using edge triggered flip flop or Master slave J-K flip-flop or by using the clock signal whose pulse width is less than or equal to the propagation delay of flip-flop.

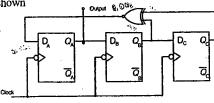

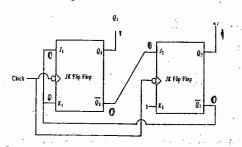

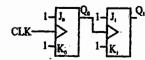

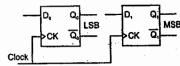

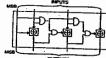

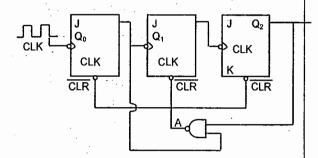

- → Master-slave flip-flop is a cascading of two J-K flip-flops Positive or direct clock pulses are applied to master and these are inverted and applied to the slave flip-flop.

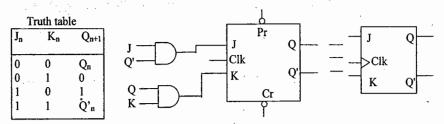

- → D-flip-flop: It is also called a Delay flip-flop. By connecting an inverter in between J and K input terminals, D flip-flop is obtained. K always receives the compliment of J.

→ D flip-flop is a binary used to provide delay. The bit on the D line is transferred to the output at the next clock pulse.

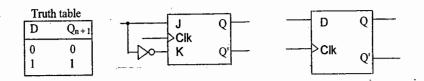

\* T flip-flop: J K flip-flop can be converted into T-flip-flop by connecting J and K input terminals to a common point. If T = 1, then  $Q_{n+1} = Q_n$ . This unit changes state of the output with each clock pulse and hence it acts as a toggle switch.

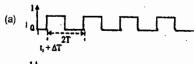

If X KHz clock signal is applied to a T flip-flop when T = 1, then the output (Q) signal frequency is given by X/2 KHz. Thus it acts as a frequency divider.

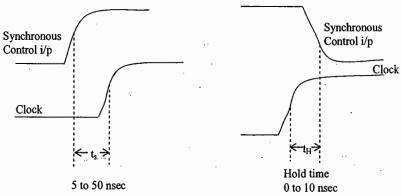

Setup Time (t<sub>s</sub>): Time interval immediately preceding the active transition of clock signal during which the control input must be maintained at the proper level.

Hold Time (t<sub>H</sub>): The time interval immediately following the active transition of the clock signal during which the synchronous control input must be maintained at the proper level.

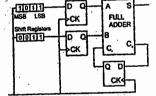

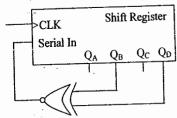

#### Registers and Shift Registers:

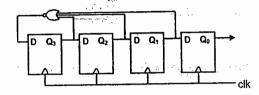

- → A register is a group of flip-flops used to store binary information. An n-bit register can store n bit information.

- → A register which is able to shift the information either from left to right or from left to right is called a shift register.

#### → Shift register can perform four different operations.

- 1. Serial input Parallel output.

- 2. Serial input Serial output

- 3. Parallel input Parallel output

- 4. Parallel input Serial output.

- → Universal Shift Register: A register which is able to shift the information form left to right or from right to left and which can perform all four operations is called universal shift register.

#### → Applications of Shift registers :

**ACE Academy**

- 1. Serial to parallel conversion (It is also called spatial to temporal code conversion)

- 2. Parallel to serial conversion (It is also called temporal to spatial code conversion)

- 3. Sequence generator.

- 4. Multiplication and Division.

- 5. Ring counter and Twisted ring counter.

- 6. Digital delay line ( serial input and serial output operations

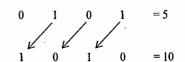

- → Left shift operation is nothing but multiplied by 2.

Eg:

$$Q_3$$

$Q_2$   $Q_1$   $Q_0$

Shift left by n-positions is equivalent to multiplication by 2<sup>n</sup>.

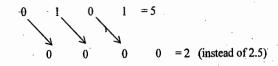

→ If least significant bit = 0, then right shift operation by one position is same as Division by 2.

Eg:

$$Q_3 \ Q_2 \ Q_1 \ Q_0$$

$$1 \quad 0 \quad 1 \quad 0 = 10$$

$$0 \quad 1 \quad 0 \quad 1 = 5$$

If L.S.B = 1, then right shift operation gives integer division by 2.

- → Ring Counter: Shift register can be used as ring counter when Q₀ output terminal is connected to serial input terminal.

- → An n-bit ring counter can have "n" different output states. It can count n-clock pulses.

- → Twisted Ring counter: It is also called Johnson's Ring counter. It is formed when Q<sub>0</sub>' output terminal is connected to the serial input terminal of the shift register.

- → An n-bit twisted ring counter can have maximum of 2n different output states.

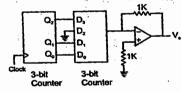

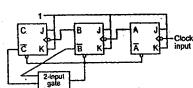

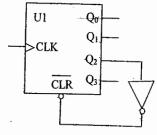

#### **COUNTERS:**

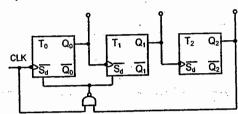

The Counter is driven by a clock signal and can be used to count the number of clock cycles. Counter is nothing but a frequency divider circuit.

- → Two types of counters are available :

- 1. Synchronous.

- 2. Asynchronous.

- → Synchronous counters are also called parallel counters. In this type of counters the clock pulses are simultaneously applied to all the flip-flops.

- → Asynchronous counters are also called Ripple or serial counters. In this type of counters the output of one flip-flop is connected to the clock input of next flip-flop and so on.

- $\rightarrow$  A counter having n-flip-flops can have  $2^n$  output states i.e. it can count  $2^n$  clock pulses (0 to  $2^n$ -1).

- → The largest binary number that can be represented by an n-bit counter has a decimal equivalent of  $(2^n-1)$ . Example: n=3, then  $2^n-1=2^3-1=7$ .

- → A counter can be made to count either in the up mode or in the down mode.

- → Synchronous counters are faster than asynchronous counters.

- → The modulus of a counter is the total number of states through which the counter can progress. For example mod-8 counter is having 8 different states (000 to 111).

- $\rightarrow$  The output signal frequency of Mod-n counter is  $1/n^{th}$  of the input clock frequency. Hence that counter is also called  $\div$  n counter.

- → The number of flip-flops (n) required to construct Mod N counter can be obtained from the following formula:

$$2^{n-1} < N \le 2^n.$$

- → A decade counter is also called Mod- 10 or ÷10 counter requires 4 flip-flops.

- → Any binary counter can be a modulus counter where as the modulus counter need not be a binary counter.

- → Six flip-flops are required to construct mod-60 counter.

#### S V Rao

#### POINTS TO REMEMBER:

Chapter - 7

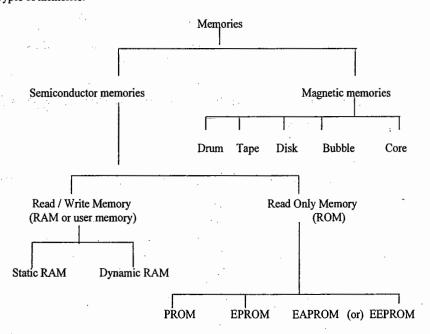

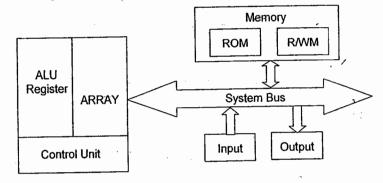

- → The digital computer memory can be classified into two types: Primary memory or main memory and Secondary memory or Auxiliary memory.

- → Primary memory or main memory: The memory, which is directly accessible to the CPU, is called main memory. Eg: ROM, RAM.

- → Secondary memory or Auxiliary memory: The memory, which is not directly accessible to the CPU, is called secondary memory. Eg: Hard disk, Floppy disk, Magnetic tape etc.

- → Primary memories are semiconductor memories. They are available in the form of integrated circuits with different memory capacities.

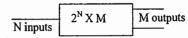

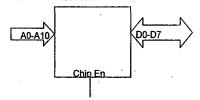

- → The capacity of a memory IC is represented by 2<sup>n</sup>xm, where '2<sup>n'</sup> represents number of memory locations available and 'm' represents number of bits stored in each memory location.

Eg: 2<sup>10</sup> x 8 = 1024 x 8.

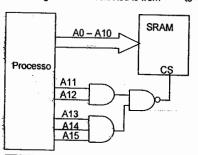

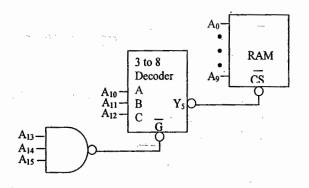

- → The number of address bits required to identify 2<sup>n</sup> memory locations are "n".

Eg: to identify one out of 1024 (2<sup>10</sup>) memory locations, 10-address bits are required.

- → Assigning addresses for different memory locations of a memory IC is called memory mapping.

- → To increase the bit capacity or length of each memory location, the memory ICs are connected in parallel and the corresponding memory location of each IC must be selected simultaneously.

- Eg: 1024 X 8 memory capacity can be obtained by using four memory ICs of memory capacity 1024 X 2.

- → To increase the number or memory locations (i.e. explanation of memory), the memory ICs are connected such that at any time only one memory IC must be selected.

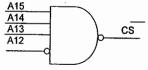

Eg: To get 4kX8 memory capacity, it is required to use four 1kX8 memory ICs, and at any time one of four memory ICs can be selected using a decoder.

- → The number of memory Ics of capacity 1kX4 required to construct a memory of capacity 8k X 8 are 16.(i.e.16 memory Ics of 1kX4 capacity are required to construct 8kX8 memory).

#### Memory device parameters or characteristics:

- → Access time: The access time of a memory is defined as the time required to access a memory location for reading or writing.

- → The access time of a magnetic drum is defined as the sum of seek time and transfer time.

- → Access rate: It is defined as the reciprocal of access time. It is measured in words per second.

- → Access time depends on the physical characteristics of the storage medium, and also on the type of access mechanism used.

- → Access models: An important property of a memory device is the order or sequence in which information can be accessed.

- → Random Access: It the access time is independent of position of the memory location, then it is called random-access mode. I.e. The access time of every memory location is same.

Eg: ROM, CAM (content addressable memory)

- → Sequential Access: A memory in which the locations can be accessed in a sequence only is referred to as a sequential memory. Ex: Magnetic tape, magnetic bubble

- → Some memory devices such as magnetic disks or drums contain a large number of independent rotating tracks. If each track has its own read-write head, the tracks may be accessed randomly, although access within each track is serial. In such cases the access mode is same times called semi random or direct access.

- → Alterability: The method used to write information into a memory may not be irreversible, in that once information has been written, it can not be alterable while the memory is in use i.e. on-line.

- → Memory whose contents can not be altered on-line are called ROM's.

- → ROMs whose contents can be changed are called PROM's.

- → Memories in which reading or writing can be done on-line are called R/W Memories.

- → Volatile memory: In this type of memory, the stored information is dependent on power supply i.e. the stored information will remains as it is as long as power is applied Eg: RAM.

- → Non-volatile memory: In this type of memory, the stored information is independent of power supply. I.e. the stored information will present as it is even if the power fails.

Eg: ROM, PROM, EPROM, EPROM etc.

PROM: Programmable Read Only Memory

EPROM: Erasable programmable Read Only Memory

EPROM or EPROM: Electrically Erasable Programmable Read Only Memory

EAPROM: Electrically Alterable Programmable Read Only Memory

- → Static RAM (SRAM): In this type of memory binary information is stored in terms of voltage. SRAMs stores ones and zeros using conventional Flip-plops.

- → Dynamic RAM (DRAM): In this type of memory, binary information is stored in terms of charge on the capacitor. The memory cells of DRAMs are basically charge storage capacitors with driver transistors. The presence or absence of charge in a capacitor is interpreted as logical 1 or 0.

- → Because of the leakage property of the capacitor, DRAMs require periodic charge refreshing to maintain data storage.

- → The package density is more in the case of DRAMs. But additional hardware is required for memory refresh-operation.

- → SRAMs Consume more power when compared to RAMs. SRAMS an faster than DRAMs.

- → Destructive Read Out Memory: The memory is known as destructive Read Out (DRO) memory if the reading method destroys its contents. For such memories each read operation must be followed by write operation to restore the contents. Ex. Magnetic Core.

Chapter - 8

- → Non-destructive Read Out (NDRO): It is called NDRO if the reading operation does not change its contents. Ex: Magnetic tapes, disks, RAMs, ROMs, etc.

- → Semiconductor technologies used for fabrication of memories are

(a) Bipolar and (b) Unipolar (i.e. MOS)

- → CCD (charge coupled Device) is a volatile memory and sequential access-type.

- → Low cost and high access rates are desirable memory characteristics.

- → By changing the hardware logic used for the chip selection of memory IC, it is possible to change the memory mapping.

Notes:

S V Rao

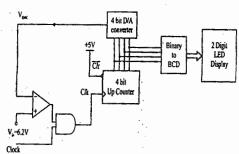

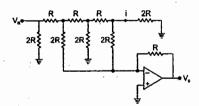

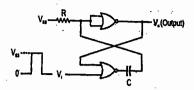

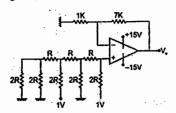

- → Digital to analog conversions needed in digital data processing requires insulation of digital information to an equivalent analog information.

- → Digital to analog converters, may be used to translate the output of a digital system into an analog form for the purpose of driving a pen recorder or for a cathode ray oscilloscope.

A / D & D / A CONVERTERS

- → The D/A converter is commonly referred to as a decoding device, since it is used to decode the digital signals into proportional voltage or current signals for an entry into an analog system.

- → D/A converter converts digital information into corresponding analog signals.

- → There are two types of DAC's are available

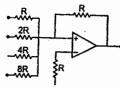

- a) Binary weighted resistors type of DAC and

- b) R-2 R ladder type of DAC

- $\rightarrow$  The R 2R ladder type of DAC is superior type of DAC.

- → Binary weighted resistors type of DAC has many drawbacks.

- → When the number of input bits is large, the resistors used for LSB has to be very large value.

- → Each resistor required in the network is of different value, as such the resistors used are to be chosen from wide range of values.